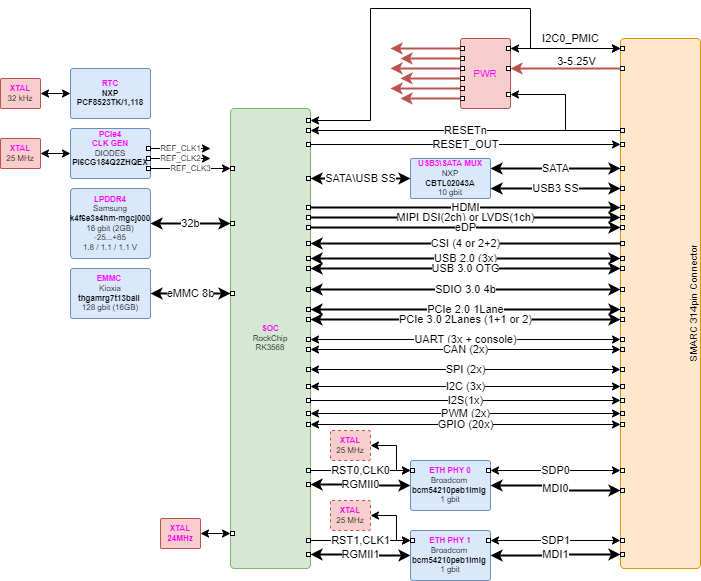

Таблица 1: Основные технические характеристики

| Внешние разъемы | Краевой разъём в соответствии со SMARC, по стандарту (2.0\2.1) |

|---|---|

| Процессор | RK3568 |

| Ядра:4х-ядерный 64х-битный Cortex-A55, 22нм техпроцесс, частота до 2.0ГГц | |

| Графический ускоритель: ARM G52 2EE, поддержка OpenGL ES 1.1/2.0/3.2, OpenCL 2.0, Vulkan 1.1 | |

| Видеоускоритель: аппаратное декодирование 4K 60к/с H.265/H.264/VP9, аппаратное кодирование 1080P 100к/с H.265/H.264, 8M ISP, HDR | |

| Нейросопроцессор: 0.8Tops@INT8, интегрированнный высокопроизводительный AI ускоритель RKNN NPU, поддержка Caffe/TensorFlow/TFLite/ONNX/PyTorch/Keras/Darknet | |

| ОЗУ | Память LPDDR4 2 ГБайт (512M x 32) (MT53D512M32D2DS-053WT:D) |

| Флэш-память | Память eMMC 16 ГБайт (THGAMRG7T13BAIL) |

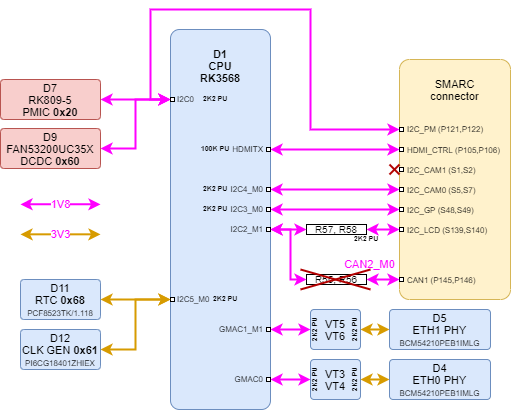

| ИС управления питанием | PMIC (RK809-5) |

| Прочие компоненты | Часы реального времени RTC (PCF8523TK) |

| 2x Гигабит ETH PHY (BCM54210PEB1IMLG) | |

| PCIe CLK GEN 25 MHz XTAL→4x 100MHz (PI6CG18401Z) | |

| Переключатель SATA → USB3 1:2 (CBTL02043A ) | |

| Интерфейсы | 1x USB 2.0 |

| 1x USB 3.0 OTG | |

| 1x USB SS | |

| 1x PCIe 2.1 | |

| 2x PCIe 3.0 | |

| 2x CAN | |

| 3x UART + 1x отладочный UART | |

| 2x SPI | |

| 3x I2C | |

| 1x I2S | |

| 2x PWM | |

| 1x SATA | |

| 1x HDMI | |

| 1x eDP | |

| 1x MIPI DSI or LVDS | |

| 1x SDIO | |

| 2x ETH 1GB | |

| 20x GPIO | |

| Напряжение питания | +5 Вольт |

| Потребление | TBD |

| Габаритные размеры | 82×50 мм |